Machine Instructions

What is a Digital Computer?

A computer that takes input in a binary form and produces output in binary form.

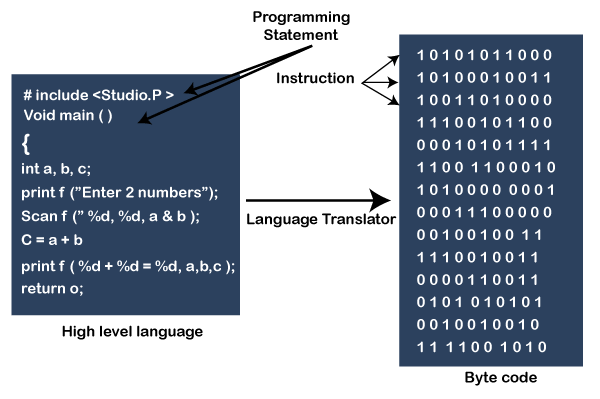

The question arises of what kind of input the computer takes or what kind of input’s required for the computer to work on. So inputs are two things Programs + data, programs are the Machine instructions, and to execute these instructions, data is required. The computer understands only binary form, all the instructions should be in the binary, but instruction cannot be written in binary directly by the user. The program is written in High-level language, and translated with the help of a compilation processor program. So with a language translator, the program is compiled into an equivalent program in binary form. This is called a low-level program or machine code, Byte code, object code.

Program (instructions) written in High-level language are called programming statements. Instructions are the statements which CPU understands, and the CPU understands only binary, so instructions are compiled into binary bits that are understandable by the CPU.

Definition of Instruction: A group of bits that instruct the computer to perform some operation. Binary bits statements instruct the computer to execute the program.

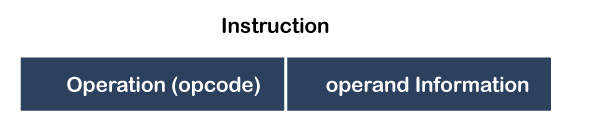

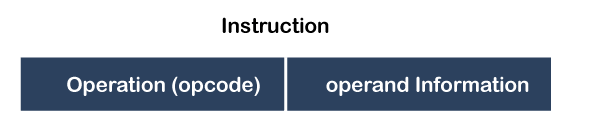

The general format of instruction

Instruction can contain two types of information.

- Operation – It denotes what kind of operation the instruction wants to perform. The first few bits will inform the CPU that this operation to be performed to execute this instruction. Operations like ADD, MUL, SUB, MOVE, STORE, LOAD etc. So, the starting part of the operation will indicate operation, and it is called Operation Code, or in short, it is called OpCode.

- Operands – It is the remaining part of the instruction that tells the CPU about the operand’s data on the basis of which an operation is executed.

For example: A CPU has 8 Bits instruction, 3 bits are for the opcode, and the remaining 5 bits are for operand information.

Maximum combination for opcode- 23 =8(0000, 0001, 0010, 0011…1111)

It means 8 distinct types of instruction CPU can support.

Let's take two instructions ADD R1, R2, R3 and ADD R1, R3, R5. Here both have ADD type instruction operands that may be different, but the instruction type is the same.

Note: One opcode denotes one single operation within the CPU. During designing CPU, number of opcodes are decided by architecture. The compiler generates distinct types of instructions that are generated by the CPU.

Instruction Set Architecture (ISA)

The collection of all those types of instructions that the CPU can support is known as Instruction set architecture. For the above example, size of ISA is 8.

Types of Instruction (Based on Operations)

- Data Transfer: MOV, LDA, IN, OUT, PUSH, XLAT, XCHG, POP, LEA

| MOV | Move byte or word to memory. |

| XLAT | Translate byte using a look-up table |

| PUSH | Push data/word into the stack |

| POP | Pop word out of the stack |

| IN | Input byte |

| OUT | Output word to port |

| LEA | Load effective address |

| LDS | Load pointer using data segment |

| XCHG | Exchange byte/ word |

- Arithmetic and Logic: ADD, SUB, AND, OR

| ADD, SUB | Addition and Subtraction of byte |

| CMP | Compare byte/ word |

| NEG | Negate byte/word |

| INC, DEC | Increment and Decrement |

| IMUL | Integer multiply |

| IDIV | Divide Byte |

| CBW | Convert byte to word |

| CWD | Convert word to double word |

- Machine Control: EI, DI, PUSH, POP

| EI | Enable instruction |

| DI | Disable instruction |

| PUSH | Put the word into the stack. |

| POP | Put the word out of the stack. |

- Iterative: LOOP, LOOPE, LOOPZ

| LOOP | The logic of Object-Oriented Programming |

| LOOPZ | LOOP While Zero |

| LOOP | LOOP While Equal |

- Branch: JMP, CALL, RET, JZ, JNZ

| JMP | Jump |

| CALL | Produce call |

| RET | Return instruction |

| JZ | Jump If Zero |

| JNZ | Jump If Not Zero |

Types of Instruction( Based on Operand information)

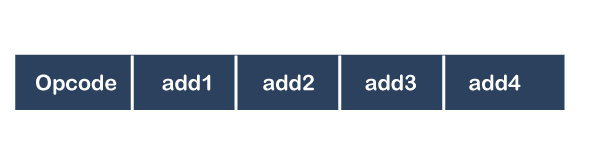

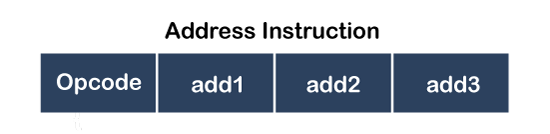

- 4- Address Instruction

Within each instruction, maximum of 4- addresses can be specified.

The opcode is the mandatory part of the instruction; we have 4 addresses in which staring three addresses specify operands and last address specify the address of next instruction. The program counter is not present in CPU having 4- address instruction format. Nowadays, it is not used in computers due to disadvantages.

Disadvantage

- Larger size instruction

- Larger size program in memory

- Relocation is not easy.

- Instruction fetch takes more time.

- 3- Address Instruction

The modern computer uses this 3- address instruction format. Within each instruction, maximum of 3- addresses can be specified.

The opcode is the mandatory part of the instruction; we have 3 addresses that specify operands, and the program counter is used in CPU. Intermediate code generation, 3- address code is generated because CPU can Implement 3- address code in terms of instruction directly, and CPU is also using 3- address instruction code. All those disadvantages in 4- address instruction is eliminated here.

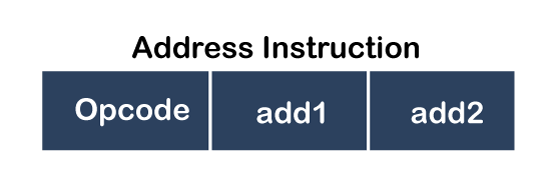

- 2- Address Instruction

Maximum 2 addresses can be specified within an instruction. One operand is used as source and destination. Both means instruction is taken from R2, and the result is copied to R2.

The disadvantage of 2-Address instruction

- More number of instructions for a program as compare to 3-address instruction format. So it requires more memory.

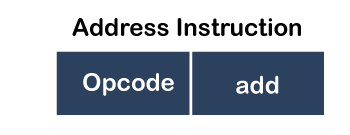

- 1- Address Instruction

Maximum 1 address can be specified within an instruction. Here apart from opcode, we have only one operand, but we also require a second operand to do the operation, so here second operand value comes from Accumulator. So, it is supported in Accumulator based architecture.

Disadvantage

- It will have more instruction for a program than 2-address instruction because addresses and more operands are not specified.

- Here, the number of instructions is reduced, only one operand is used, but we still have more instructions than 2 and 3 address instruction.

- 0- Address Instruction

0-Adress instruction follows stack-based architecture. No addresses can be specified within instruction, and there is only one opcode. So two operands are implicitly taken from the stack. Therefore, 0- address instructions are implemented on stack-based architecture. It is not used in nowadays systems.

Note: If a CPU supports 3-address instruction, then it supports 2-1-0 address instruction also.

If a CPU support 2-address instruction, then it supports 1-0 address instruction also.

If a CPU support 1-address instruction, then it supports 0-address instruction also.

If a CPU supports 0-address instruction, it can only support 0 address instruction.