Addressing Modes

Introduction: Addressing Modes

An instruction consists of two parts opcode and operands. Opcode tells the operation going to perform, and operand information is the address of the operand. The CPU interprets this address in many ways, so to solve this confusion, some extra bits are used within the instruction. These extra bits are a mode field used before the address to help the CPU explore how to use the address field to get the operand correctly.

Definition: Addressing mode specifies how and from where the operand is obtained using the address field value of instruction. It tells “how to use this address part so that CPU can get the operand" or to understand the address part of the instructions.

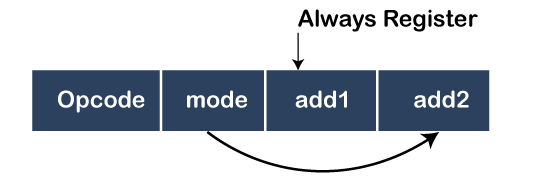

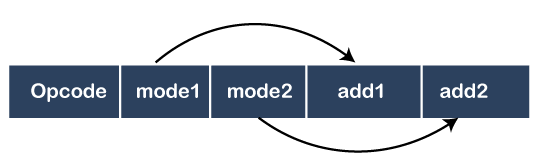

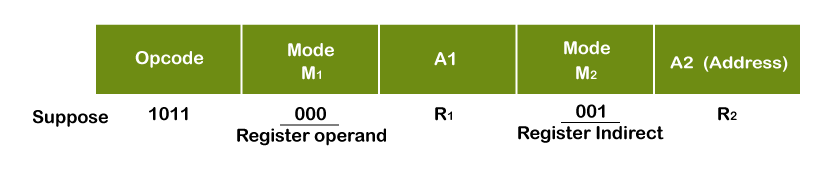

There can be two options for the 2- address instructions.

Here, one mode specifies how to use one address. It says Add1 is always for the register, and mode is used to specify how to use Add 2.

Here, mode1 will be used to specify add1, and mod 2 will be used to specify add 2.

Addressing modes will provide the following information to the system:-

- Counters for loop control and a pointer to the memory

- It does program relocation.

- It does indexing of an array.

- Addressing modes helps in creating records/ structures.

- They provide fast execution when compared to a certain mode of the operand.

- Shorten the instruction length (bit size of the instruction).

- Few bits in the address part represent a certain address mode.

Modes are classified in two ways:-

- Computable- These are the kind of computations required to get the effective address for multiplication, division, addition and subtraction.

Kinds of modes incomputable:-

- Auto increment/ Decrement

- Indexed mode / Register

- Index + Base register Mode

- Index + Base register + Displacement Mode

- Scaled Mode

- PC relative Mode

- Base relative Mode

Non- computable- These kinds of modes do not perform computation. So no computation occurs. Kinds of modes in non-computable:-

- Implied Mode

- Immediate Mode

- Register Mode

- Register Indirect Mode

- Direct Mode

- Indirect Mode

Types of Addressing Modes

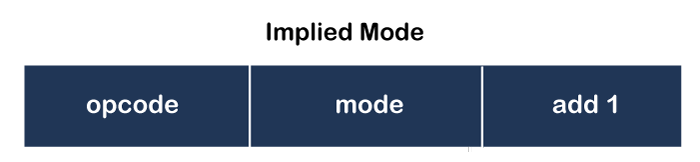

- Implied Mode

In this addressing mode, opcode definition also specifies the operand. As we know that anyway, opcode specifies the operation, but here it specifies operation also. Therefore, an address is not required here.

For example- (i) Suppose opcode is increment accumulator (INCA) in the instruction. In this increment is the operation, the accumulator is the operand and special purpose register, which does not require any address. An exact address is not required; the CPU can access all those special-purpose register implicitly. Here accumulator is accessed implicitly by the CPU.

(ii) CMA à it is complement AC. This opcode itself mentions that it complements the content of the AC register, so there is no need to specify the operand's address. CMA= 101 =010

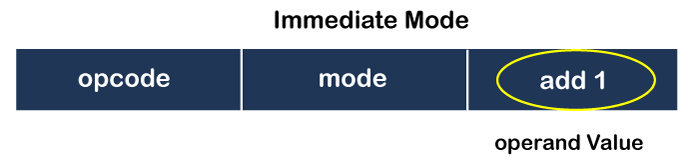

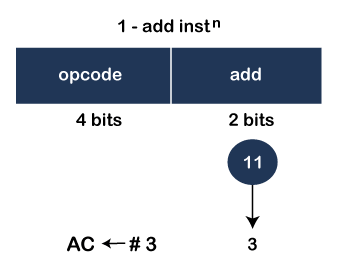

- Immediate mode

Definition:- The address field of instruction specifies operand value.

Address part = Operand

This addressing mode says that the CPU will interpret the address part as the operand. Whatever is written in the address part is taken as the operand value for the operation.

For example:-

- ADD#500, 500 is not an operand address or effective address, but it is just operand(constant).

- This 3 is my operand value, which is copied in the accumulator. Immediate mode is used to initialize the register with a constant value.

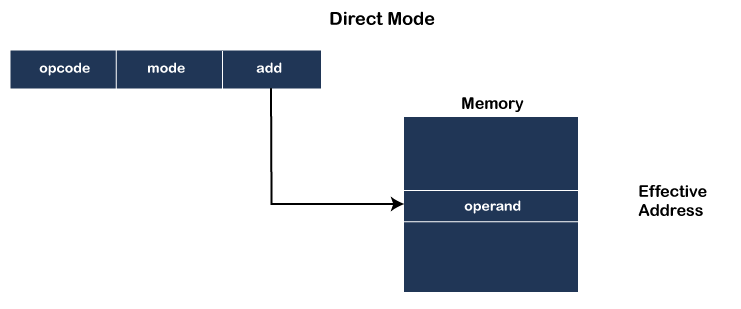

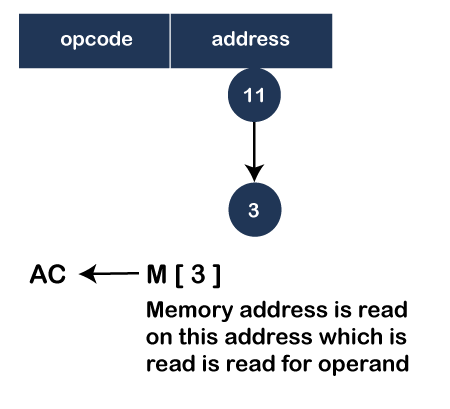

- Direct Mode

In the instruction, whatever the address field is specified, that is the memory address. With the particular address, we can fetch the operand from memory. The operand address is called the effective address. So, an effective address is present in this address field. This direct mode is also known as Absolute mode.

For example, in this example, ACß M[3] represents the memory address read on this address.

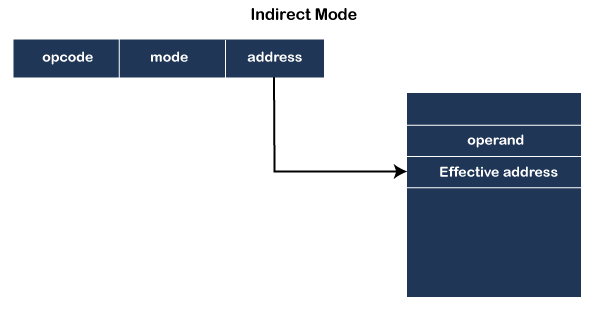

- Indirect Mode

In this addressing mode, we get the address indirectly. With the help of address present in instruction, we can fetch the effective address present in the memory. After reading the effective address we can get the operand located somewhere in the memory. The address field of instruction specifies the address of the effective address.

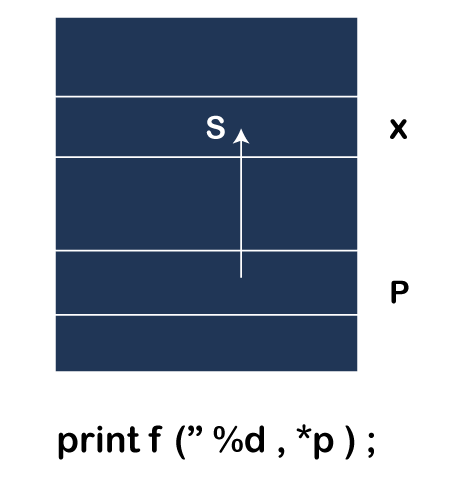

Advantage:- Indirect mode is used to implement the pointer.

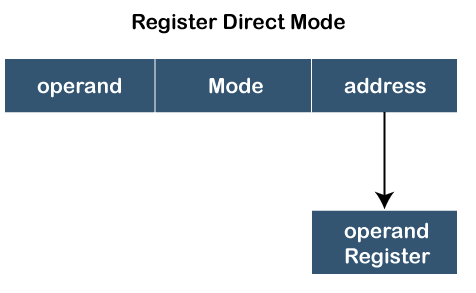

- Register Mode/ Register direct mode

Definition:- In this Addressing Mode, the address part of the instruction specifies a register, which holds the operands. It is also called register direct mode (get operand from register).

Example:- ADD R1

R1 = effective address; from this address, we get the direct operand.

ADD = This instruction causes the CPU to add the content of the accumulator to the content of the register R1

i.e. ACCß [ACC] + [R1] (content in R1)

Note:- Address specified in the instruction is the register address.

Designated address need to be in register.

Faster execution because there is no need to fetch an address from the memory.

Register direct mode cannot be used if the operand moves from register to memory.

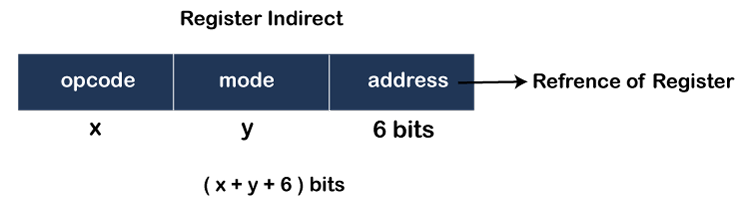

- Register Indirect Mode

Definition:- In this Addressing Mode, the address field of instruction specifies a register, and the register holds an effective address that holds the operand.

ADD R1, R2

This mode is used to shorten the instruction length, and it is explained with an example.

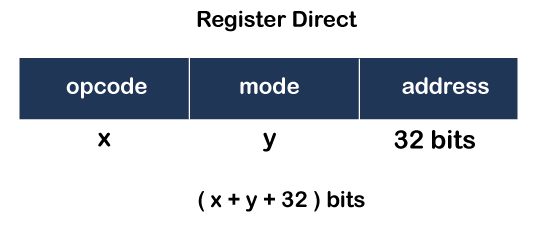

Example for register direct or indirect mode

Assume a system with 4 GB of main memory and CPU has 64 GPRs,

Main memory address= 32 bits, register reference = 6 bits

Solution: direct mode instruction is written like this:-

Here, the opcode is x, the mode is y, and the address is 32 bits =(x+y+32) bits.

And for indirect mode, instruction is written like this:-

Here, the opcode is x, the mode is y, and the address is 6 bit =(x+y+6) bits.

(x+y+6) bits have less size, and we can save 3 bit here. Therefore, it decreases the instruction size.

Operand access time with the same instruction

For Direct mode = 1 memory access time (using the address to access the operand)

For indirect mode = 1 memory access time + 1 register access time

- 1 register access time is very tiny time, so it is negligible time)

Hence, equal time is required to access the operand.

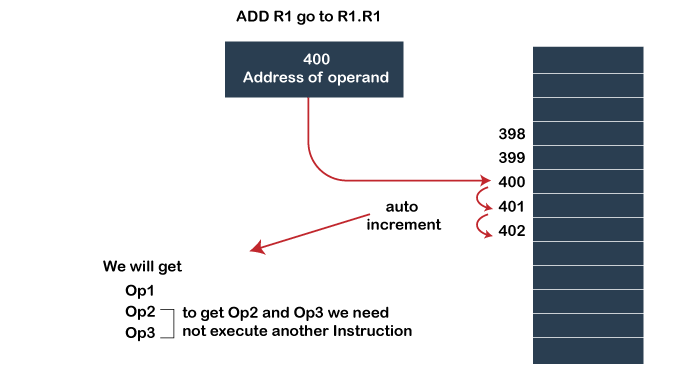

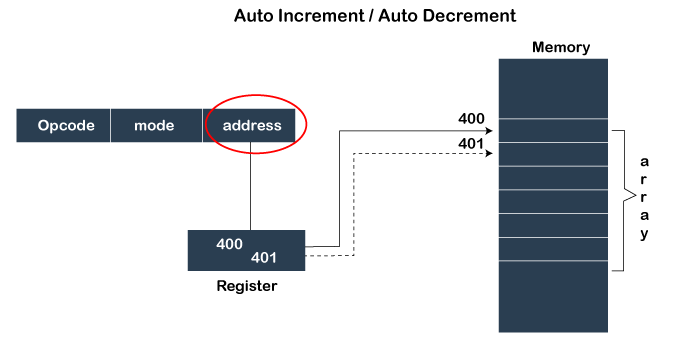

- Autoincrement/ Auto decrement mode

These addressing modes are used to access the table of content (array) sequentially. It is a variant of Register Indirect Mode, and in this content of the register, the effective address is automatically incremented or decremented.

- The amount of increment depends on the size of the data item accessed.

- When the address in the register is used to access memory, the value in the register is incremented/decremented by one automatically, i.e., without using ALU because the counter can be incremented or decremented.

- This addressing mode is used to access the table of operands from memory by incrementing or decrementing the effective address.

- For example:- In the given figure, an instruction ADD R1 is given to the system, which indicates an addition to the R1 register directly without providing an address. Address already stored in register is taken as operand address and incremented or decremented automatically.

- Displacement addressing mode

In this addressing mode, effective address is given with the combination of address part and register.

Effective Address = Address part + Register

Address part = Address or Offset/ Displacement

Register = Offset or Address

Based on the above formula and logic, there are three addressing modes given below:

- Index mode.

- Base register addressing mode.

- Relative addressing mode.

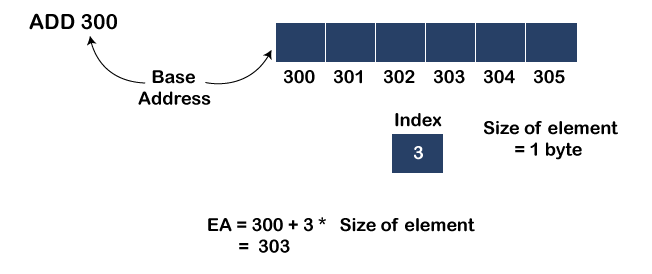

- Index Mode/ Index Register Mode

Index Register is a special register of CPU that contains index value. Index mode is used to access an array element. In this, we use indexed register instead of Program Counter.

Effective Address = Index (Constant value) + Content of Register

Note: If we know the base address of an array and the element's index value, then we can find that particular element address.

Effective Address = Base address of array + offset (Index Register)

The content of the index register is added to the address part of the instruction.

For example:- Let's take two instructions.

- LOAD R1, X(Ri) { x(ri) is index i.e. constant}

EA = X + [Ri]à content of register [ suppose 5]

- LOAD R2, A(R1) { A(R1) is the memory address}

EA = A + [R1]

- Example:- ADD 300

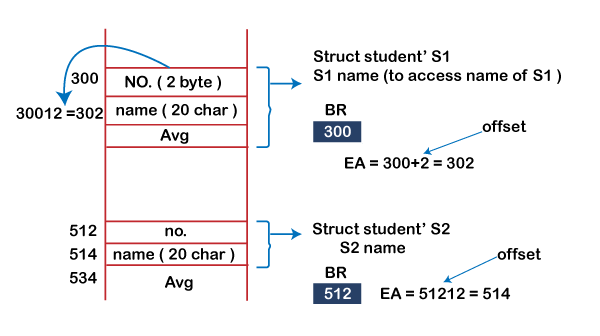

- Base Register Addressing Mode

Base register addressing mode contains the base address of structures. If the base address is in the base register, we can access two structures with the same Offset.

Offset is the address part, register is the base register that holds the address.

Effective address = Address part + Register

EA = Offset + BR (base register)

For example: Base register addressing mode allows implementation of records/ structures.

One block is created into memory for structure/ record.

Note: In a base register addressing, the register contains a base address and the instruction address part contains offset but in the indexed addressing mode, the register contains offset(index), and the address part of instruction contains the base address. However, the overall effective address will be the same after addition.

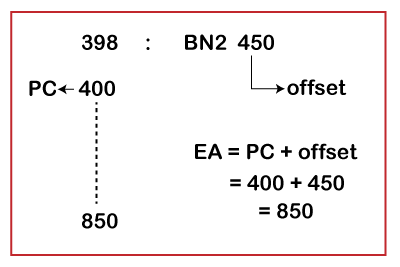

- Relative / PC- Relative addressing mode

Relative addressing mode allows the implementation of branching/ target address; if our programming language supports control statements, loops, and conditions, then relative addressing mode is required. We can write position-independent code called relative code.

Effective Address = Offset + PC/ Address(register will give address)

Offset = Offset is the distance address from the current address to the target location.

For example: Using relative addressing, we can reach the target address.

Advantage: Relative addressing mode is faster than the direct and indirect addressing mode.

Case: Indirect addressing mode

Let's assume the target address is 850

Instruction: 398: BNZ 450; { 450 is the offset}

Now PC will hold the address of the next instruction{398………850}

EA = PC + Offset = 400 + 450 = 850 {Here I memory cycle +1 ALU opn s required, therefore it is faster than the indirect addressing mode.

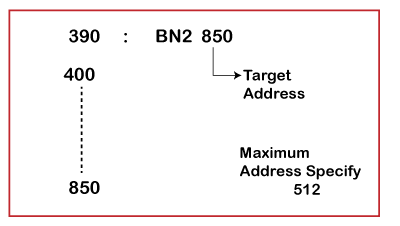

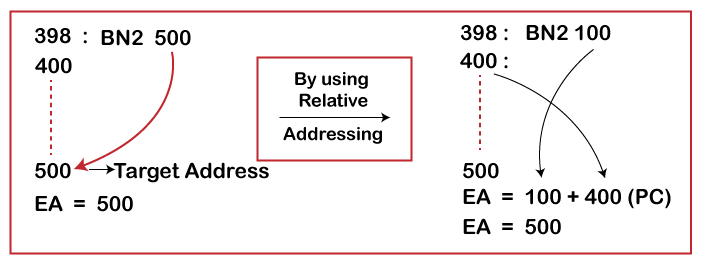

Case: Direct addressing mode

With direct addressing, we get the full address of instruction from (0-511) i.e. 512, but the target address is 850. So, with direct addressing, it is not possible. With indirect addressing, we can do this but 2 cycles are required.

With direct addressing, we can solve the question like this:-

The way the operands are chosen during